Electronic Systems

Parallel Ultra-Low-Power Laboratory (PULP Lab)

Scientific Coordinators: Prof. Luca Benini, Prof. Davide Rossi, Prof. Francesco Conti

The focus of the PULP lab is energy efficiency for digital circuits over a very wide operating range, starting from small devices with a power budget of less than a mW that will drive Internet of Things (IoT) applications, all the way to High Performance Computing (HPC) systems such as data centers that consume power in the MWs.

Limitations in available energy for mobile devices, maximum power density in tightly integrated circuits and the significant costs associated with running and cooling data centers all require solutions where circuits need to be able to do more with available energy than ever before. The research in the group concentrates on improving this efficiency by at least an order of magnitude which will be the key to enable digital solutions of the future.

We improve energy efficiency by embracing parallelization, by making sense of data close to where it is produced thereby reducing the communication overhead, by making the best use of the latest technological developments in integrated circuits and by designing heterogeneous systems where customizable accelerators enhance general purpose processing.

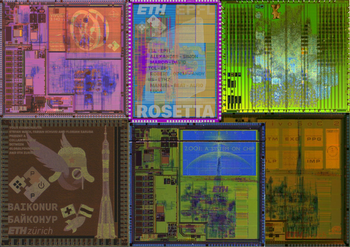

The flagship project of the group is PULP (Parallel Ultra Low Power) platform which is a cluster based system, where each cluster consists of small and efficient processors that have access to a common data memory which allows parallel single cycle access as long as there are no contentions. When the workload is favorable, cores are operated at near threshold voltage where the efficiency is the highest, or are completely switched off when they are not needed. We also take advantage of what state of the art manufacturing technologies can provide, such as using extended body biasing techniques enabled by the FDSOI process for example. When used in combination, all these techniques allow us to increase the efficiency of the system far above what was possible before, and we plan to reach and exceed 1 Gops/mW over a large operation range on a programmable architecture in the coming years.

The group covers all aspects of digital system design from technological aspects, circuit and architecture design, demonstrators for various applications, all the way to how these new systems can be programmed. Application fields include biomedical devices, smart sensors, video processing, telecommunication and high-performance computing.

The group has a long tradition of designing integrated circuits, with more that 30 chips manufactured during last 10 years. We use the latest technologies available to universities in the world (such as the STM 28nm FDSOI since 2014), and through a series of lectures we allow all interested students to design and test their own digital circuits in 65nm technology. The group has

collaborations with major semiconductor industries such as STMicroelectronics.

Design of integrated circuits for low power IoT and analog in-memory computing for edge-AI applications

Scientific Coordinators: Prof. Antonio Gnudi, Prof.ssa Eleonora Franchi Scarselli

The research concerns the design of integrated circuits for low power consumption and high computation efficiency. The activities are carried out within the joint STMicroelectronics – ARCES lab.

Main activities:

- Design of integrated circuits for ultra-low power receivers (Wake-up Radios). Wake-Up Radios are used in IoT nodes to reduce the power consumption of the synchronization and communication processes. They are always-on receivers with the main task of continuously monitoring the wireless channel waking-up the microcontroller and the main radio only when a wake-up signal is received. Trade-offs between power consumption and sensitivity are considered in the circuit design of the Analog Front-End. Techniques of clock and data recovery are implemented in the digital baseband unit to minimize the number of false wake-up signals. The circuits are designed and manufactured in STMicroelectronics technology and are used in IoT system prototypes.

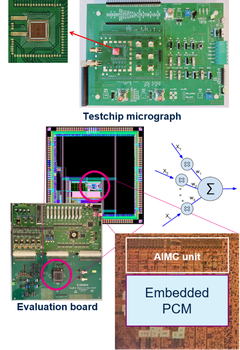

- Design of circuits for in-memory computing applications using arrays of Phase-Change non-volatile Memories (PCM). Starting from standard embedded PCM arrays, architectures and circuits are developed for analog in-memory computing (AIMC) for edge-AI applications and neural networks. The goal is to perform computations in an efficient way directly on the IoT node, by avoiding the energy bottleneck of standard digital processing unit, where data have to be moved back and forth between memory and processor. An AIMC prototype has been designed in STMicroelectronics 90-nm CMOS technology + GST PCM cells.

Related Projects: EnABLES, R3-PowerUP, StorAIge, NeuroSoC

Energy harvesting systems and micro-power management circuits

Scientific Coordinators: Prof. Aldo Romani, Prof. Marco Tartagni

Development of electronic systems and integrated circuits for energy harvesting and micro-power conversion, based on piezoelectric, thermoelectric, photovoltaic, and RF transducers.

The paradigms of pervasive and ubiquitous electronics still require advancements in circuit architectures with ultra-low intrinsic power consumption. Energy autonomy should be achieved by extracting power from environmental energy source such as piezoelectric, thermoelectric, photovoltaic, and RF transducers, as well as by managing and distributing ultra-low power to system components while performing efficient sensing and communication.

This research projects aims at the development of sustainable energy harvesting and micro-power conversion circuits in both discrete electronics and integrated circuit (IC) implementations. The activities carried on within this research are:

- modeling and characterization of energy transducers;

- design of innovative and efficient circuits for micro-power conversion and management

- the minimization of intrinsic consumption and reduction of the start-up voltage of power conversion/management systems;

- reduction of the energy requirements of sensing and communication circuits by pursuing optimal hardware/firmware design trade-offs

- the development of minimally invasive wireless sensor nodes with ultra-low consumption for environmental monitoring, wearable electronics, and energy efficiency in buildings;

- the design of battery-less and wirelessly powered sensor nodes operating at long distances from their RF power source, with a focus on sensors nodes powered on-demand and on the design of smart passive EPC GEN2 RFID tags including enhanced sensing and localization capabilities.

Related Projects: EnABLES, CONNECT, CONVERGENCE, PROGRESSUS, Energy-ECS.

Structural Health Monitoring

Scientific Coordinators: Prof. Alessandro Marzani, Prof. Luca De Marchi

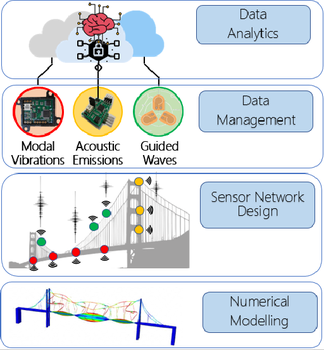

SHM refers to the process of implementing methodologies and technologies for damage detection, localization, characterization and severity evaluation in structures and industrial equipment such as bridges and buildings as well as pressure vessels. Damage is defined as a change to the material and/or geometric properties, including changes to the boundary conditions and system connectivity, which adversely affect the system's performance. In this context, our aim is the implementation of embedded, cheap and miniaturized sensor nodes and sensor networks with multi-sensing capabilities. In particular, our sensor nodes can be configured to measure accelerations, acoustic emissions, tilts, temperatures, sound, impedances, among others, using MEMS. Our applications span from operational and vibration modal analyses, high frequency stress waves for acoustic emission, guided waves based applications. Regarding these two latter fields of application, in particular, our group has developed transducers are able to generate and detect directional ultrasonic guided waves within a structure with minimal hardware requirements thanks to a novel patented procedure.

Operation, control and protection of power distribution networks, microgrids and local energy communities

Scientific coordinator: Prof. Alberto Borghetti

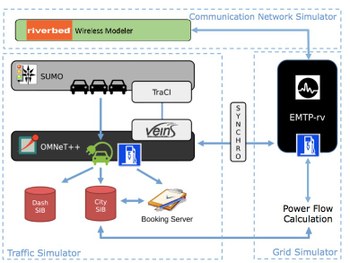

Current research activities concern - optimization models and distributed approaches for the reactive power scheduling in medium voltage and low voltage distribution networks; - electromobility impact on the operation of urban electric power networks and coordination strategies of charging stations; - scheduling of storage resources in local energy communities; - mitigation of the frequency variations in microgrids after the transition between grid-connected mode and island operating mode; - fault protection of medium voltage distribution networks with loop and mesh configuration.

Other information is available in the web site of the laboratory LISEP (Power System Laboratory of the University of Bologna) : http://lisep.ing.unibo.it.

Related Projects: E2SG, CONNECT, WInSiC4AP, PROGRESSUS.